Overview

Steady-state thermography is limited to detecting hot spots that heat up a minimum of 100 mK (0.100°C). This may be useful for locating shorts on high-power devices but is inadequate for detecting low power defects such as semiconductor device leakage current or short circuit with very low or very high resistance. Steady-state thermography also suffers from poor spatial resolution as the heat from localized hot spots diffuses rapidly, blurring the location of the heat source.

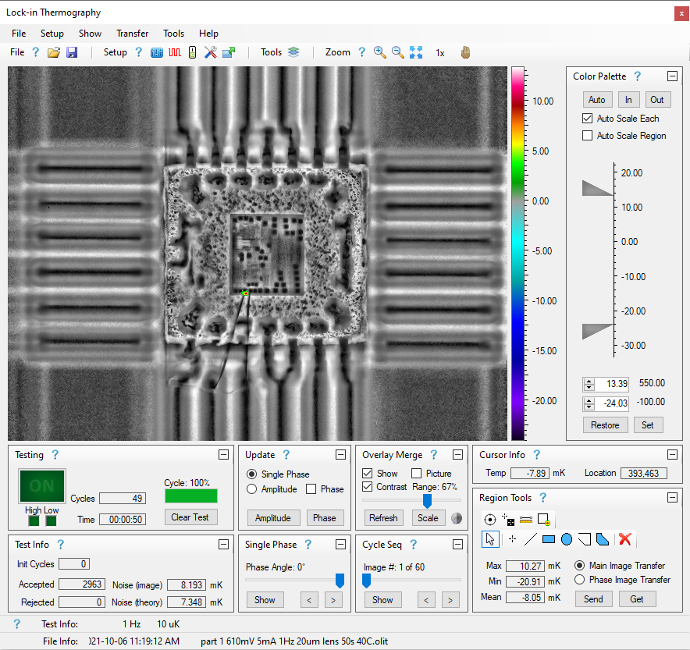

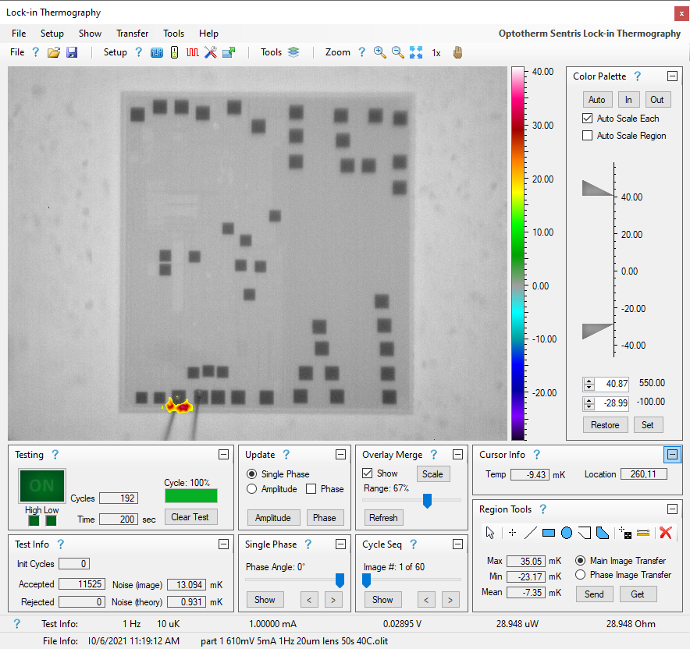

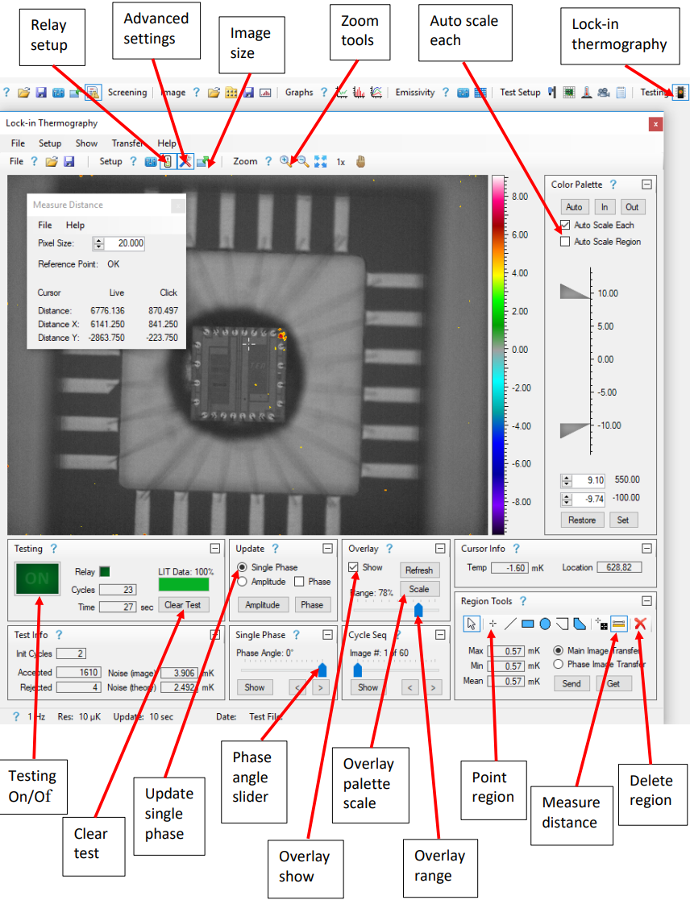

Lock-in thermography is a process of automatically and repeatedly applying voltage to a device at regular intervals using a laboratory voltage source while the temperature response of the device is integrated and analyzed over time. Over many power cycles, the sum of thermal images captured while the device is unpowered are subtracted from the sum of thermal images captured while the device is powered. Using this technique, hot spots that heat up less than 1mK (0.001°C) and dissipate below 10 µW can be detected. Increasing the number of test cycles results in improved test sensitivity and weak sources of heat arising during normal operation of the device can even be detected.

The frequency at which voltage is cycled can be set from below 1 Hz up to 15 Hz. Performing lock-in tests at lower frequencies improves test signal/noise due to higher device heating. Higher frequency tests improve hot spot spatial resolution by reducing thermal diffusion into adjacent areas of the device.

Instrument Control

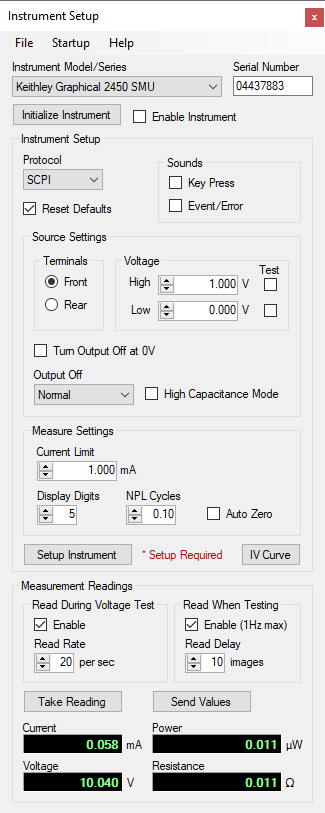

Lock-in thermography is a process of automatically and repeatedly applying voltage to a device at regular intervals using a laboratory voltage source while the temperature response of the device is integrated and analyzed over time. The Instrument Setup window within Thermalyze is used to setup and control a Keithley voltage source (such as a source measure unit) via USB interface.

Voltage can be cycled between zero volts and a higher voltage, or between two non-zero voltages. Current flow and applied voltage are read from the instrument and displayed at the bottom of the window. To help operators determine appropriate test voltage, current limit and test time, fail site power dissipation and resistance are calculated and displayed.

Thermalyze Software: See Thermalyze Operation documentation for Instrument Control software features and operation.

Supported Instrument Models

See Thermalyze documentation for a list of supported instrument models.

IV Curve Plotting

Plot the device current response to an applied voltage range.

Supported Instrument Models

- Keithley graphical SMU (source measure unit) models 2450, 2460, 2461, and 2470

- Keithley series standard 2400 source measure units (requires National Instruments USB GPIB controller model GPIB-USB-HS+)

- Keithley series 2280 DC power supplies

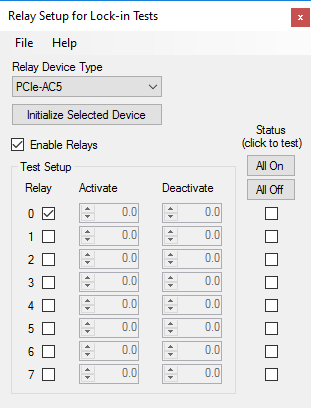

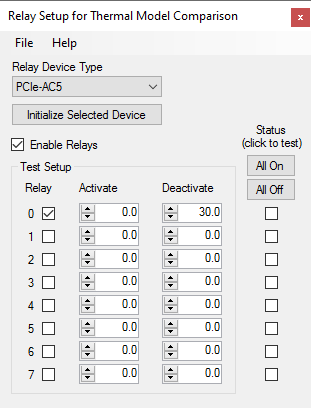

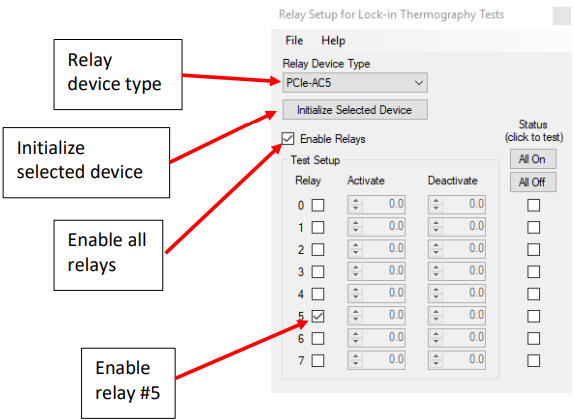

Relay Control

Lock-in thermography is a process of automatically and repeatedly applying voltage to a device at regular intervals using a laboratory voltage source while the temperature response of the device is integrated and analyzed over time. High frequency (up to 15 Hz) or high current (up to 6 Amp) mechanical relays can be used to control voltage from your existing source meter or power supply. Relay outputs can also be used to trigger external test equipment when more sophisticated device voltage control is required. Mechanical relays have zero leakage current in the off state which is advantages when performing lock-in tests on devices with low leakage current.

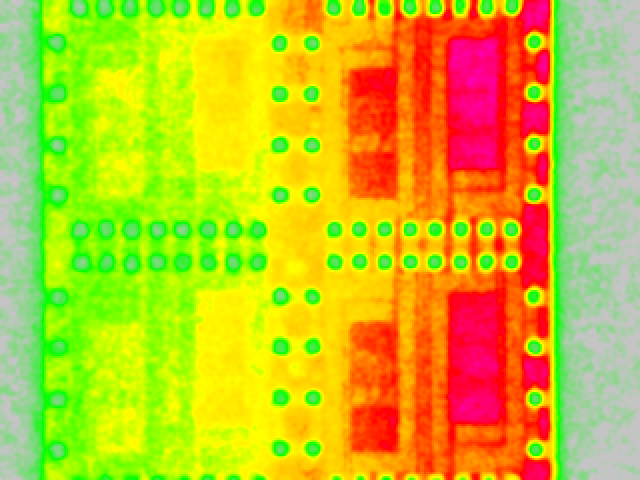

Test Images

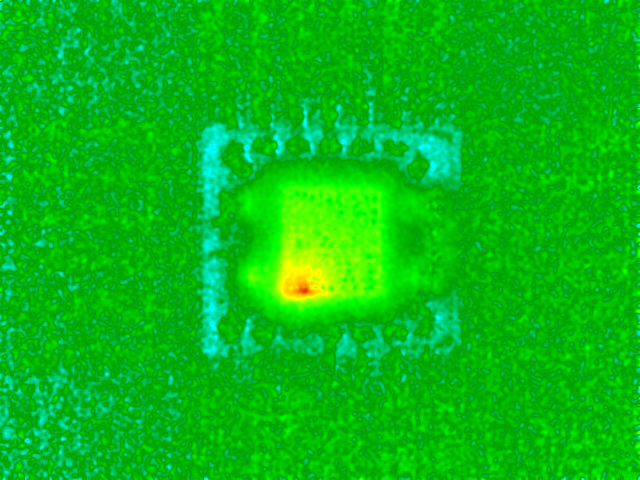

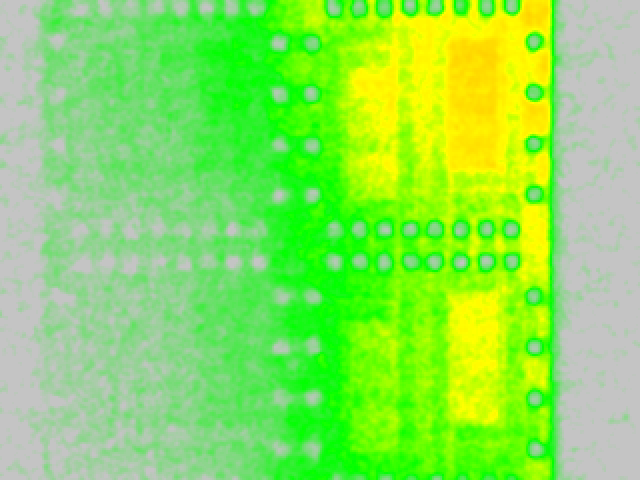

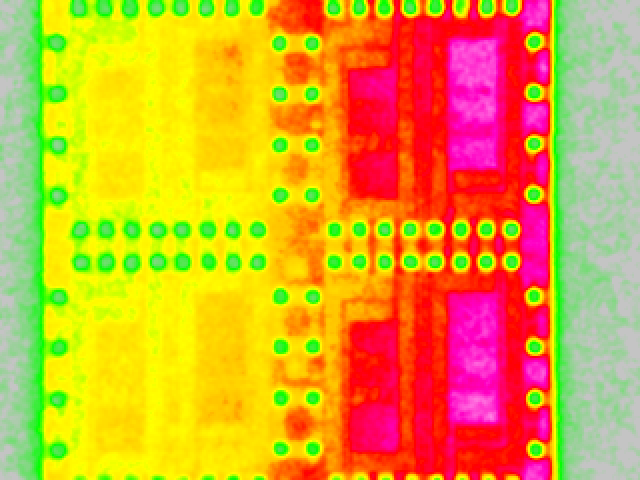

Single Phase Image

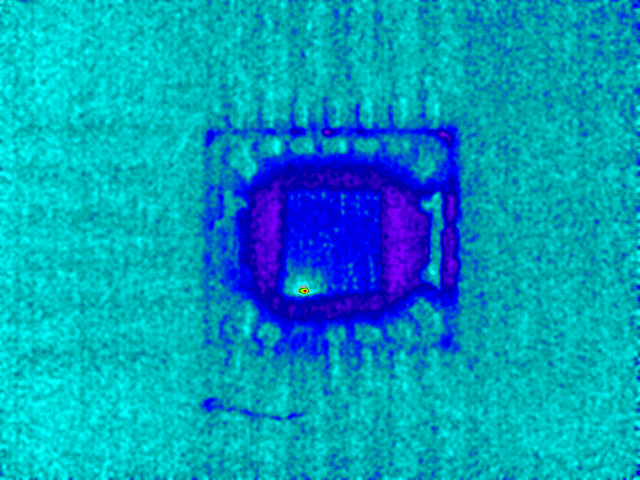

A single phase image displays temperature increases at a specific time in the cycle. The time within the cycle is expressed using phase angle with 0 degrees representing the beginning of the cycle when voltage is applied and -180 degrees representing when voltage is removed. A phase angle of -360 degrees represents the end of the cycle and is equivalent to a phase angle of 0 degrees.

Single phase images are used to locate faults in the xy direction. They can also identify areas that heat up at different times within the cycle providing a correlation with defect depth. Single phase images typically produce the highest xy spatial resolution of all Lock-in images.

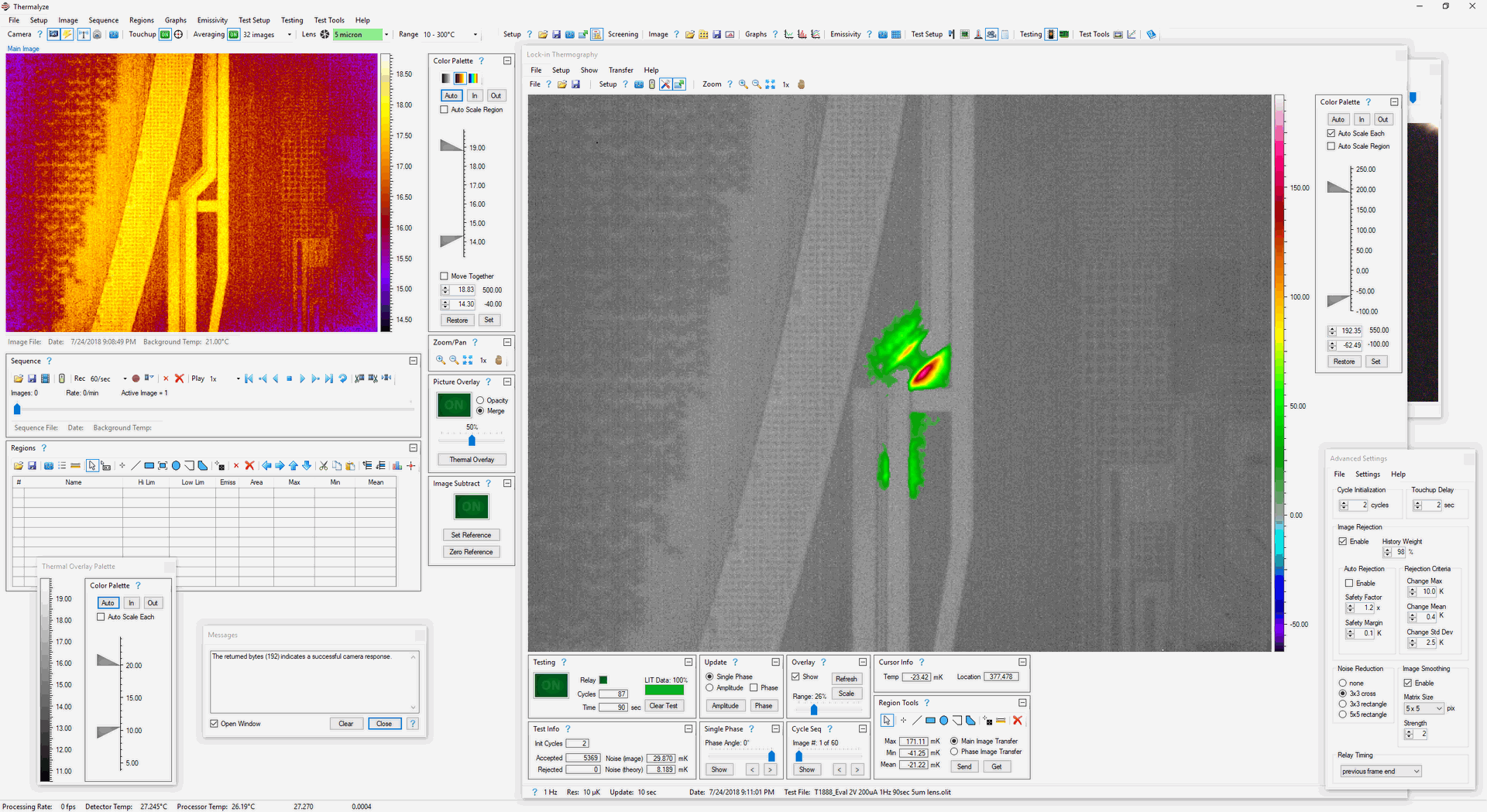

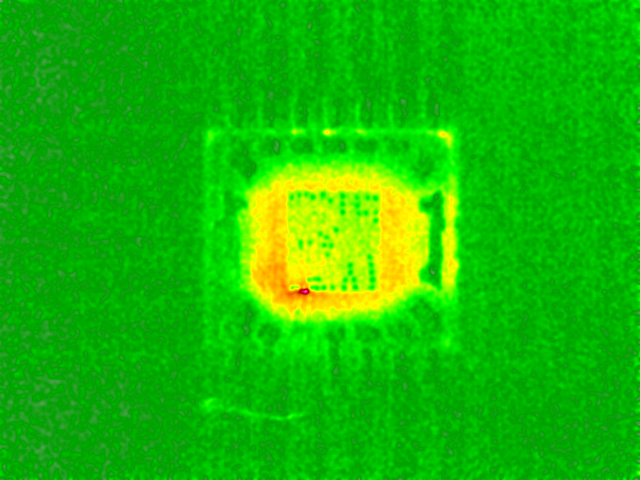

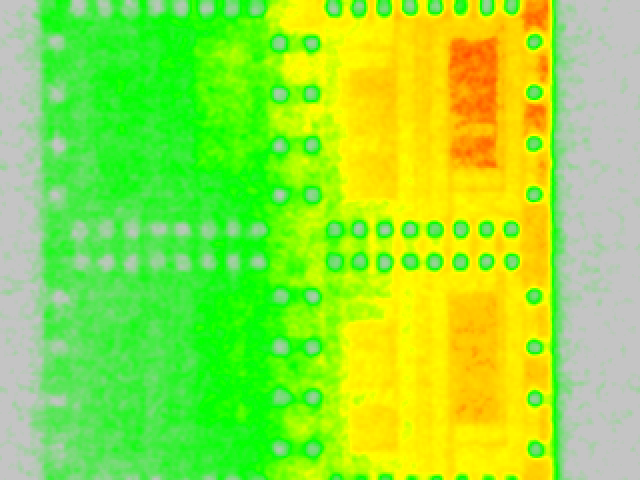

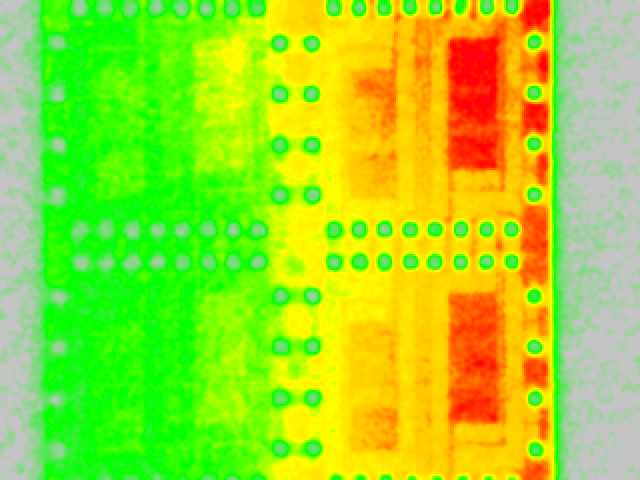

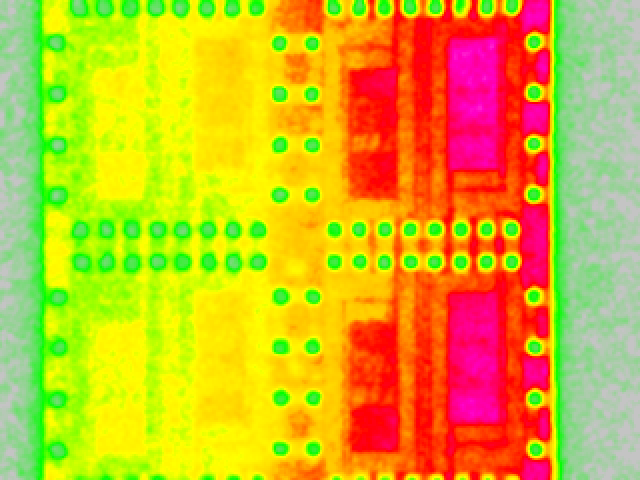

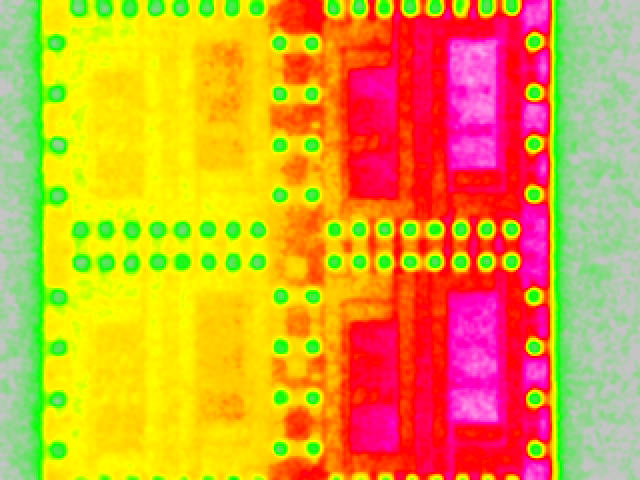

Amplitude Image

An amplitude image displays all temperature increases at any time during the cycle and is commonly used to determine fault location in the xy direction.

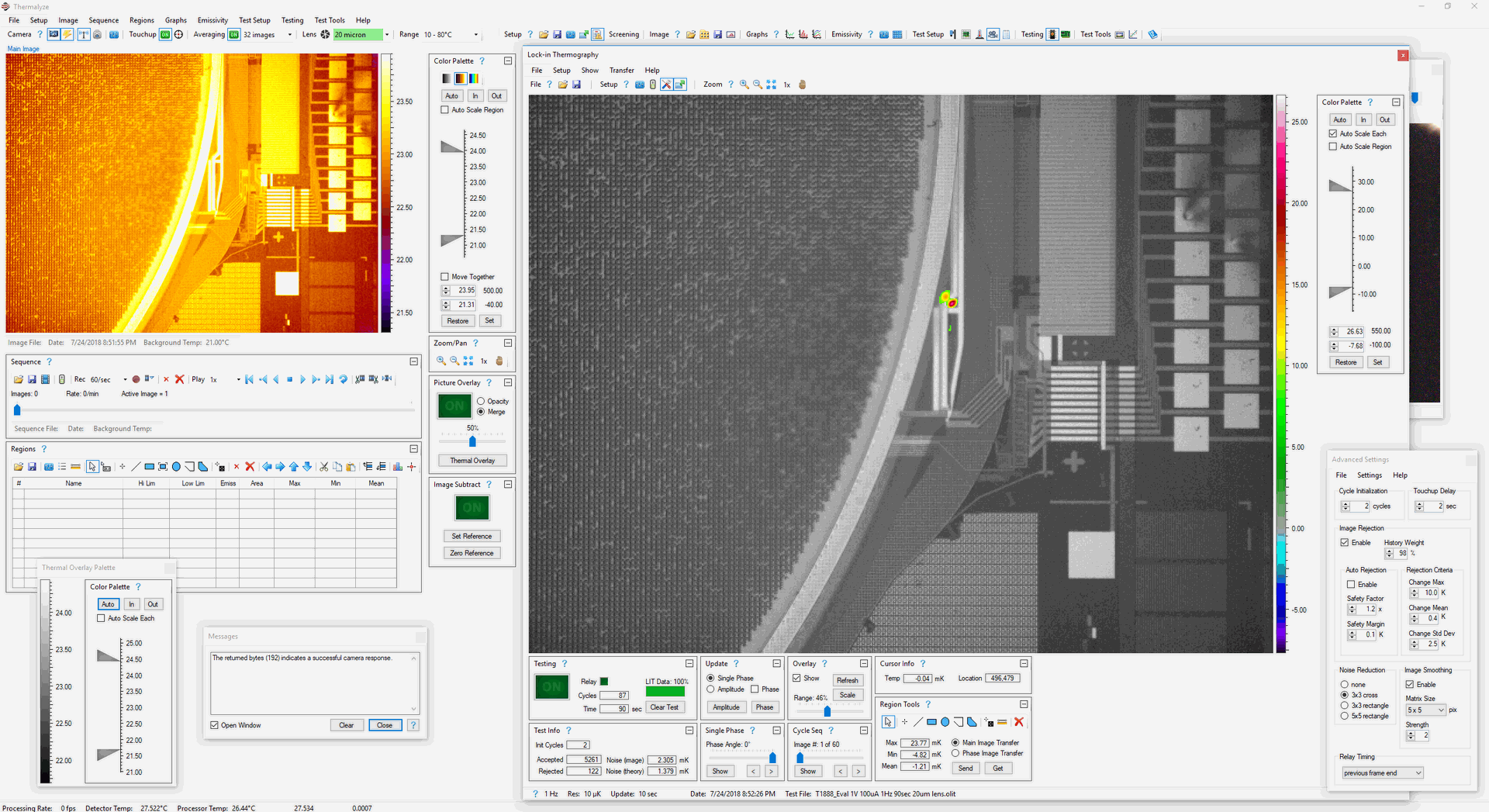

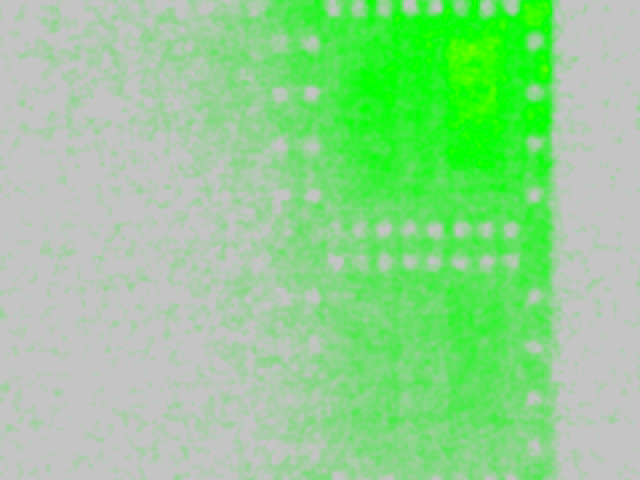

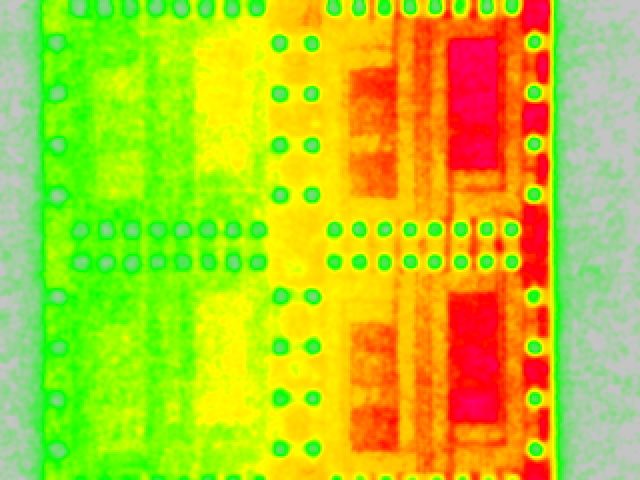

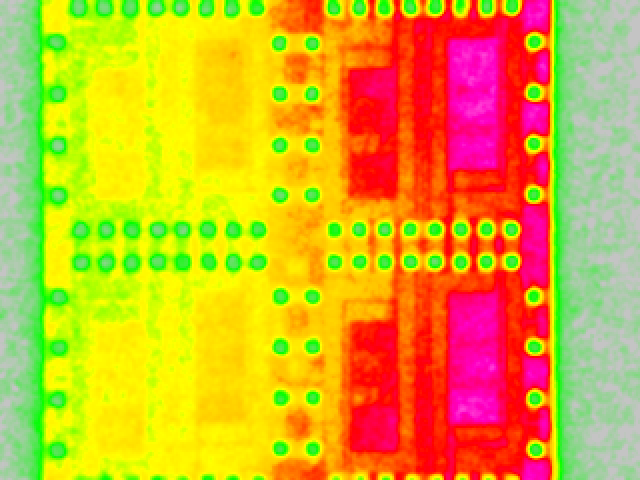

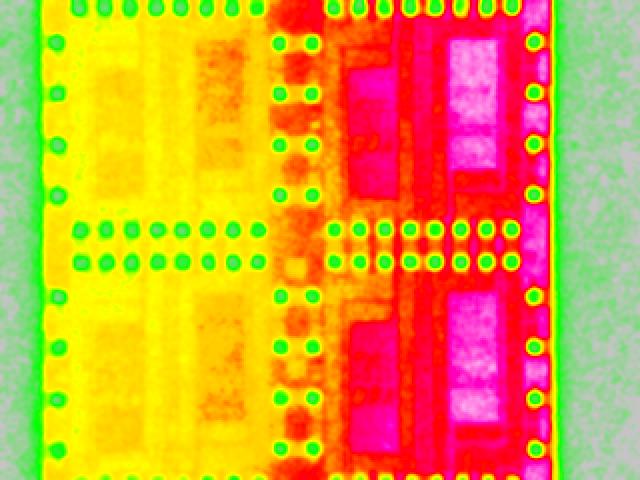

Phase Angle Image

The phase image displays the phase angle of heating at each point in the image. Phase angle is most often associated with defect depth because heating phase angle represents the time within a cycle when internally generated heat reaches the surface. Phase angle represents the delay between powering a device and the resulting surface heating. When analyzing packaged devices and stacked die, phase angle is used to estimate the depth of a defect.

Phase angle is measured in units of degrees and has a range of 0 to -360 degrees. A phase angle of 0 degrees indicates device heating occurring immediately after power is applied and takes place at or near the surface. Negative phase angle values, such as -120 degrees, indicate device heating occurring at some time after power is applied and somewhat below the surface. Larger negative values of phase angle indicate heating occurring at even greater depths.

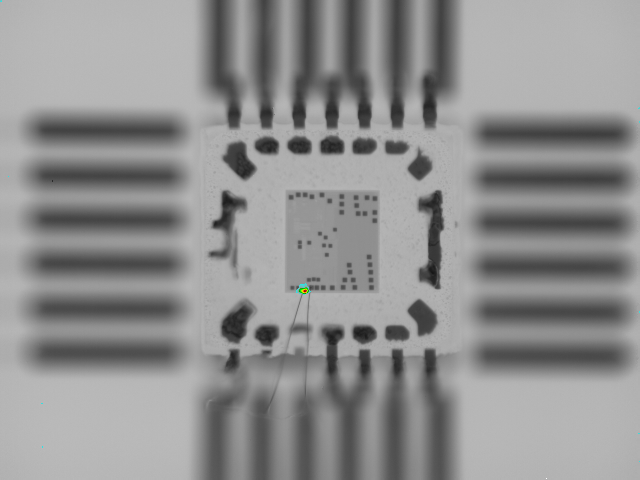

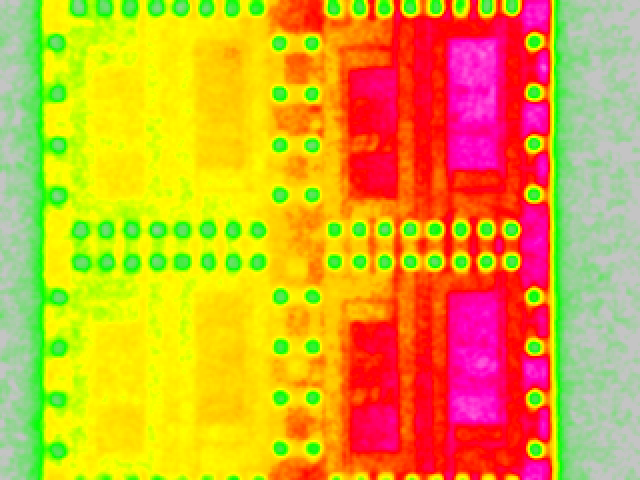

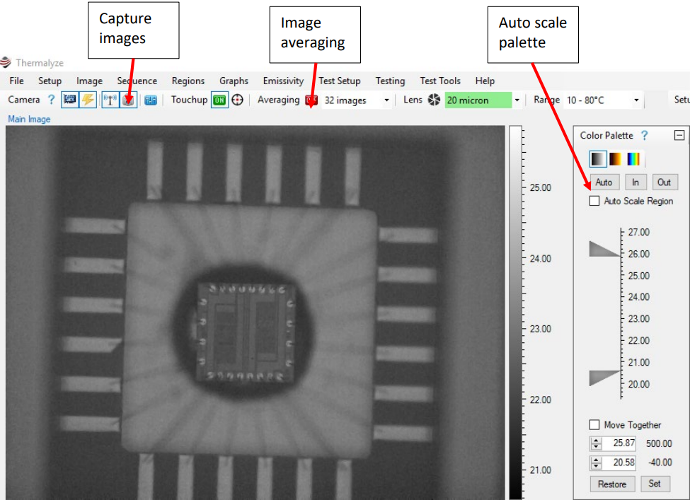

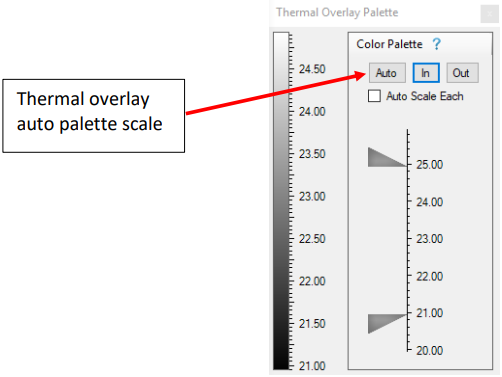

Thermal Overlay

A thermal overlay is a grayscale thermal image of the device produced by averaging all of the captured images that have been accepted in the lock-in test. When thousands of images have been accepted, the thermal overlay image noise is significantly reduced providing a high resolution image that can be merged with the single phase, amplitude, and phase angle images to facilitate locating fault xy coordinates.

Cycle Images

A cycle image displays device heating at a specific time during a cycle. Cycle images are useful for visualizing heat propagation across a device during the cycle.

Defect Depth

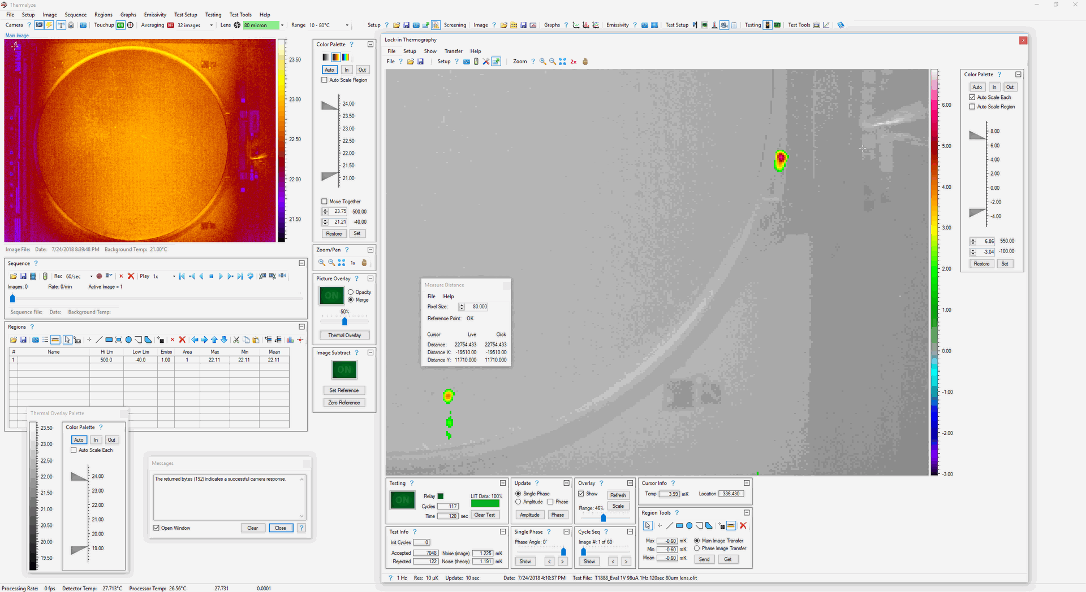

Determining fault depth in 3-dimensional system-in-package (3D SiP) devices is becoming increasingly important due to their expanding complexity and decreasing dimensions. As the number of stacked die in 3D SiP devices grows, isolating the root cause of defects within the package becomes more challenging. Sentris provides a non-destructive technique to localize the depth of faults through 3D SiP packages.

Phase Angle

Phase angle represents the time delay between powering a device and subsequent heating on its surface and can be used to estimate fault depth. The magnitude of time delay, or phase angle, is dependent on defect depth but also on the thermal conductance of materials within the device.

Phase angle is measured in units of degrees and has a range of 0 to -360 degrees. A phase angle of 0 degrees indicates device heating occurring immediately after power is applied and takes place at or near the surface. Negative phase angle values, such as -120 degrees, indicate device heating occurring at some time after power is applied and somewhat below the surface. Larger negative values of phase angle indicate heating occurring at even greater depths.

Applying Voltage

Many 3D SiP devices undergo an initialization process that is triggered at a specific voltage level. If the applied voltage is cycled between 0 and a value above the initialization voltage level, the initialization process may cause non-defect related power dissipation that can interfere with detecting the true fail site. In these cases, the device should be initialized before the lock-in test begins, and the applied voltage should be cycled between two voltages that are above the initialization voltage.

Additionally, some 3D SiP devices include on-chip voltage regulators and defect power dissipation may not correlate with on-off power cycling. In these cases, device test equipment may need to be synchronized with the lock-in cycles in order to activate fail sites.

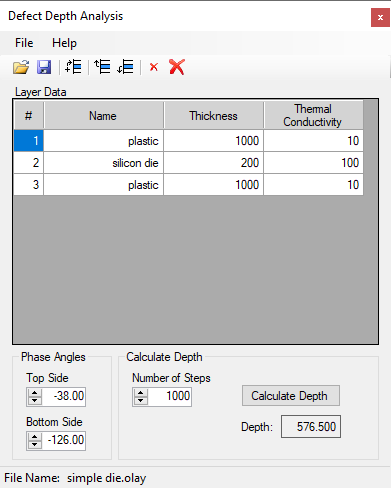

Calculating Defect Depth - Method 1

3D SiP devices are complex structures comprised of multiple stacked semiconductor die, die-attach adhesive, and package mold compound. Modelling the thermal diffusion and phase relationships of heat originating from defect sites using thermal simulation software can be very difficult.

Sentris provides a simple method to describe the internal structure of a device by entering the thickness and thermal conductivity of each material layer. Phase angle data from testing the device on both the top and bottom sides is then entered to calculate defect depth.

Calculating Defect Depth - Method 2

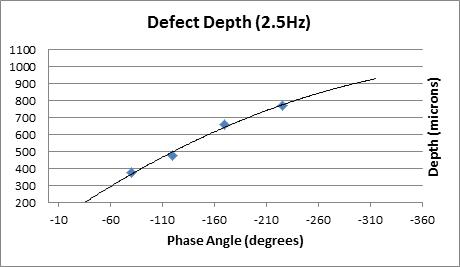

The thermal properties of die, adhesive, and mold compound are often not known precisely and the interfaces between these materials makes the problem even more complex. In these cases, it may be more effective to estimate fault depth by correlating phase angle with the depth of known internal faults.

By measuring the phase angle of faults at known depths, a relationship between phase angle and depth can be plotted. This plot can then be used to estimate the depth of unknown faults by comparing their phase angle to the plot. This method requires phase angle results from only one side (top or bottom) of a device.

The relationship between phase angle and depth is dependent on both test frequency and fault power dissipation. For this reason, the power dissipated in the defect must remain consistent when performing all tests on a specific device. A suitable frequency should be selected that results in a high plot slope but also covers all potential fault depths. This will enable differentiation between different die levels more clearly. Standard procedure is to begin testing at 1 Hz and depending on the phase results of the test, raise or lower test frequency accordingly.

Calculating Defect Depth - Method 3

This method is similar to method 2, however instead of measuring the phase angle of faults at known depths, internal reference heat sources are used. Internal I/O diodes located on multiple die levels are typically used as reference heat sources by forward biasing them. To create a defect depth plot, the device must be tested by cycling power to at least two reference heat source whose depths are known.